## Intel® Itanium(TM) Assembler

**User's Guide**

2000 - 2002

**Order Number: 712173-004**

World Wide Web: http://developer.intel.com

## **Table of Contents**

| Disclaimer                                           | 5  |

|------------------------------------------------------|----|

| OVERVIEW                                             | 6  |

| About This Document                                  | 6  |

| System Environment                                   | 6  |

| Related Publications                                 | 7  |

| Notation Conventions                                 | 7  |

| GETTING STARTED                                      | 8  |

| Environment                                          | 8  |

| Invoking IAS                                         | 8  |

| COMMAND-LINE OPTIONS                                 | 10 |

| Information                                          | 9  |

| File Handling                                        | 10 |

| Compilation Model                                    | 10 |

| Error Handling                                       | 11 |

| UNIX ABI Section.                                    | 12 |

| Advanced Section                                     |    |

| DEPENDENCY VIOLATIONS AND ASSEMBLY MODES             | 15 |

| Assembly Modes                                       | 14 |

| Mode Examples                                        | 16 |

| Serialize and Memory Syncronization Instructions     | 17 |

| Avoiding False Reports                               | 17 |

| Predicate Relation Analysis                          | 18 |

| Compare Instructions                                 |    |

| Mutex Form of the .pred.rel Annotation               |    |

| Implication Form of the .pred.rel Annotation         | 20 |

| Clear Form of the .pred.rel Annotation               | 20 |

| Mutex Relation Not Created with a Simple Compare     | 21 |

| Instructions Separated by a Predicated Branch        | 21 |

| Safe Across Calls                                    |    |

| Indirect Access to Register File                     |    |

| st8.spill and ld8.fill in the Same Instruction Group | 23 |

| FEATURES                                          | 25     |

|---------------------------------------------------|--------|

| Assembly Language Features                        | 24     |

| Instruction Set                                   | 24     |

| Bundling                                          | 24     |

| Instruction Groups                                | 25     |

| Data Allocation                                   | 25     |

| Assembly Language Directives                      | 25     |

| 64-bit Address Space                              | 26     |

| Alignment                                         | 26     |

| Assignment Statements                             | 26     |

| Aliasing                                          | 26     |

| Arithmentic Expression Handling                   | 27     |

| Complementary Features                            | 28     |

| IA-32 jmpe Instruction                            | 28     |

| instenc Pseudo-instruction.                       | 28     |

| String Equation                                   | 29     |

| Line Information for Debugging Tools              |        |

| #line Support                                     | 30     |

| Predefined Symbols                                |        |

| Virtual Registers Allocation                      |        |

| Allocate Registers                                |        |

| Declare Variables Undefine and Redefine Registers |        |

| Branch Target Annotation                          |        |

| Register Value Annotation                         |        |

| Bank Register Annotation                          |        |

| Unwind Information Generation                     | 35     |

| DIAGNOSTIC MESSAGES                               | 38     |

| Diagnostic Message Types                          | 37     |

| Diagnostic Message Syntax                         |        |

| Fatal Error Messages                              |        |

|                                                   |        |

| Error Messages                                    |        |

| Warning Messages                                  | 56     |

| RETURN VALUES                                     | 61     |

| SPECIFICATIONS                                    | 62     |

| PREDICATE ANALYSIS                                | •••••• |

| Mutex Relation                                    | 63     |

| Imply Relation                                    | 64     |

| Predicate Relation Scope                          |        |

| ( | GLOSSARY                            | 68 |

|---|-------------------------------------|----|

|   | Analysis of Combinations            | 66 |

|   | Predicate Relation Scope Exceptions | 65 |

#### **Disclaimer**

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

This Intel® Itanium(TM) Assembler User's Guide as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel, Pentium, Pentium Pro, Itanium, MMX, Xeon, Celeron, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

## **Overview**

This document describes how to use the Intel® Itanium(TM) Assembler (IAS) on Windows NT\* or Linux systems.

To gain the most from this guide, you should be familiar with the Itanium architecture and assembly language. This User's Guide documents the features specific to the Intel Itanium assembly tool. See the <u>Related Publications</u> section for references to relevant documents.

The IAS User's Guide provides the information you need to write an Itanium architecture assembly language program assembling on IAS. It describes the IAS usage and features. In addition, this user's guide provides detailed information on all IAS diagnostic messages.

IAS is a cross-platform assembler; it runs on 32-bit systems and Itanium-based systems, and produces Itanium architecture object files. IAS does not assemble IA-32 assembly language programs.

#### **About This Document**

This document contains the following sections:

- This section lists related publications and describes the notation conventions used in this manual.

- <u>Getting Started</u> describes IAS and its place in application development, and provides the IAS command-line syntax.

- <u>Command-line Options</u> explains the command-line options.

- <u>Dependency Violations and Assembly Modes</u> explains working with automatic and explicit code.

- <u>Features</u> describes the IAS features that complement the features defined in the assembly language.

- <u>Diagnostic Messages</u> lists the IAS error and warning messages.

- Return Values explains the values that IAS returns upon termination.

- Specifications lists IAS specifications.

- Predicate Analysis describes how IAS performs predicate analysis.

## **System Environment**

Hardware requirements: The recommended hardware is at least an Intel® Pentium® II processor with 256 MB memory. For extremely large input files (more than one million lines of assembly code), a 1 GB swap area is recommended.

Software requirements: Use IAS with Windows NT 4.0 or Linux.

#### **Related Publications**

The following documents provide additional information. Some of them are available at <a href="http://developer.intel.com">http://developer.intel.com</a>.

- DVLoc for Scheduling Library, document number 748283

- Intel® Itanium(TM) Architecture Assembly Language Reference Guide, document number 248801.

- Intel® Itanium(TM) Architecture Software Developer's Manual

- Volume 1: Application Architecture, order number 245317-001

- Volume 2: System Architecture, order number 245318-001

- Volume 3: Instruction Set Reference, order number 245319-001

- Volume 4: Itanium Processor Programmer's Guide, order number 245320-001

- Software Conventions and Runtime Architecture Guide, order number 245256-002

The following documents are available from Microsoft Corporation:

- *Microsoft\* Developer Studio, Visual C++\* User's Guide, LINK Reference,* Version 4.2

- Microsoft\* Portable Executable and Common Object File Format Specification, Version 4.1

#### **Notation Conventions**

This guide uses the following conventions:

This type style Indicates an element of syntax, a reserved word, keyword, a

filename, computer output, or part of a program example. The text appears in lowercase, unless uppercase is significant.

**This type style** Indicates the text you enter as input.

This type style Indicates a placeholder for an identifier, an expression, a

string, a symbol or a value. Substitute one of these items for

the placeholder.

**This type style** Indicates a placeholder for an identifier in a diagnostic

message.

[item] Indicates optional elements.

[item | item] Indicate the possible choices. A vertical bar (|) separates the

items. Choose one of the items enclosed within the brackets.

**This type style** Indicates a default or a usage example.

## **Getting Started**

The Intel® Itanium(TM) Assembler (IAS) is an assembler for the Itanium architecture assembly language. It enables full use of the architecture. It is possible to work on a Windows NT\* host to create UNIX-compatible object files.

This section illustrates the place of IAS in your application development environment, and explains how to use IAS. The subsections include:

- Environment

- Invoking IAS

#### **Environment**

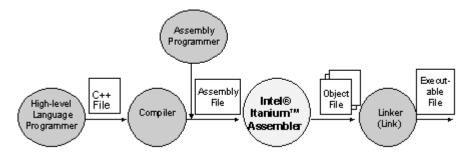

Figure below shows how IAS fits into your application development environment. IAS assembles Itanium(TM) architecture assembly language files, generated by an assembly language programmer, or a compiler. IAS generates an object file and, possibly, a diagnostics listing. The diagnostics listing includes all the error and warning messages IAS generates during assembly.

#### **Application Development**

See the *Software Conventions and Runtime Architecture Guide* for information on combining C and assembly language code in one executable file.

## Invoking IAS

To invoke IAS, use the command line:

ias [options] filename [options]

where:

options Represent the command-line options described in the following

sections. You can place any option both before and after the file

name.

filename Specifies an assembly language input file.

## **Command-line Options**

This section describes the IAS command-line options. The options are categorized into these sections:

- information

- file handling

- compilation model

- error handling

- UNIX ABI

- advanced

#### Note:

You do not have to type a space between the first letter and the letters that follow. Spaces are included here for clarity.

#### Information

The information command-line options control the data displayed on the screen and written to the diagnostics file.

[-H | -h] IAS displays a short description of all the command-line options. IAS then terminates. All other command-line options are ignored.

**Default:** Option descriptions are not displayed.

Example: ias -h

-N so IAS does not place the sign-on message with information about IAS

in the generated diagnostics file or display it on the screen.

**Default:** Sign-on appears in the diagnostics file or on the screen.

Example: ias -N so my\_file.s

-Q y AS adds the sign-on message containing information about IAS to

the .comment section of the object file.

**Default:** In ELF format the message is written, and in COFF format

it is not written.

Example: ias -Q y my\_file.s

-S nops IAS displays several figures:

- the number of nops it inserted into the code during assembly

- the number of instructions before assembly

- the percentage of nops of the total number of instructions

**Default:** Numbers are not displayed.

Example: ias my\_file.s -S nops

-v IAS prints IAS version information. Lists all libraries.

**Default:** The version information is not printed.

Example: ias my\_file.s -v

-V Prints the signon message, which is the default. Kept for backward

compatibility.

## File Handling

The file handling command-line options define the input and output files.

**-**F *OMF* This option defines the Object Module Format (OMF) of the object

file. Values for OMF are COFF32 for Windows NT, and ELF32 or

ELF64 when the targeted operating system is UNIX.

**Default for Windows NT:** COFF32

**Default for UNIX:** ELF64

Example: ias -F COFF32 my\_file.s

-I pathname AS adds pathname to an included input file search path list. This

option may be repeated to add more paths to the search list. The

paths are searched in the order listed.

**Default:** Searches for the file in the current directory only.

Example: ias -I c:\temp\my path my file.s

-o fname IAS creates fname as the object file.

**Default:** input file name with an .obj extension.

Example: ias -o my\_file.o my\_file.s

By default IAS creates my file.obj

## **Compilation Model**

The compilation model options change the default compilation values.

-M ilp\_model This option defines the address model that IAS uses. Values for

ilp\_model are:

ilp64 | lp64 | p64 – Default. Sets the address size to 64

bits. Integer and long sizes have no effect.

ilp32 – Sets the address size to 32 bits, relevant for COFF32

file format.

**Default for Windows NT:** ilp64

Example: ias my file.s -M ilp64

-M byte\_order This option sets the global default of the byte order of data allocation statements. Values for byte\_order are: le (little-endian) and be (big-endian). Use the .lsb and .msb directives to

set little or big-endian byte order for a specific section,

respectively.

**Default:** -M le

Example: ias -M be my\_file.s

-N pi IAS rejects privileged instructions. Use this option to ensure that

your code does not contain privileged instructions. **Default:** Privileged instructions are accepted.

Example: ias -N pi my\_file.s

-N IAS does not resolve global function calls. Instead you may want to

close\_fcalls use another procedure by the same name that is defined elsewhere.

**Default:** Function calls are not resolved.

Example: ias -N close\_fcalls my\_file.s

-p 32 IAS enables defining 32-bit elements as relocatable data elements.

Kept for backward compatibility.

## **Error Handling**

The error options define how IAS handles diagnostic messages.

-e fname IAS creates fname as the diagnostics file. Error and warning

messages are sent to this file.

**Default:** Errors appear on the screen (stderr). **Example:** ias -e my\_err.txt my\_file.s

-E max num IAS terminates when the number of errors IAS detects

reaches max\_num. **Default:** -E 30

Example: ias -E 3 my\_file.s

-W warning\_level IAS displays different levels of warnings. Values for

warning\_level are:

0 do not display warnings

1 display severe warnings

2 display warnings

3 display moderate warnings

4 display all warnings

x treat all warnings as errors and do not create object file if any errors detected.

**Default:** 3

Example: ias -W 1 my\_file.s

#### **UNIX ABI Section**

The following section describes command-line options specific to UNIX ABI, for restricting the floating-point register range, and defining the kernel mode calling convention. They must be used in conjuction with the -F ELF64 option.

-M rfp AS restricts floating-point registers to the range F6 - F11.

This results in less register saves and restores when entering and exiting the kernel, thereby reducing system time. Attempts to

use other floating-point registers cause an error.

**Default:** All floating-point registers can be used.

Example: ias -F ELF64 -M rfp my\_file.s

-M const\_gp IAS sets the single global pointer (GP) model in the object file.

The kernel is then considered a single model, with one GP.

**Default:** No additional flags are set in the object file.

Example: ias -F ELF64 -M const\_gp my\_file.s

-M no\_plabel IAS sets the model in the object file to single GP and no

function descriptors (plabels). As with the -M const\_gp option, the kernel is then considered a single GP and doesn't

use plabels.

**Default:** No additional flags are set in the object file.

Example: ias -F ELF64 -M no\_plabel my\_file.s

## **Advanced Section**

The following section describes some advanced options that change the assembly mode and permit virtual register allocation.

-X explicit IAS changes the default initial assembly mode from automatic to

explicit.

**Default:** IAS assembles in automatic mode.

**Example:** ias -X explicit my\_file.s For more information on dependency violations see

Dependency Violations and Assembly Modes.

-X vral IAS invokes the register allocation engine (virtual register

allocation), which allows the use of symbolic names instead of

actual register names. IAS creates a file with the suffix .vra that lists the results of all register allocations.

**Default:** Vral is not active, so the Vral syntax is not recognized.

Example: ias -X vral my file.s

-X unwind

IAS invokes the unwind generation utility. IAS builds unwind information for all procedures in the file and ignores all unwind directives.

**Default:** Unwind information is not generated. Example: ias -X unwind my\_file.s

-d debug

IAS creates Code View debug and line information for COFF32 objects. You can then use the symbolic debugger to single-step on code lines and view symbols.

**Default:** No debug and line information is created.

Example: ias -F COFF32 -d debug my\_file.s

**-**a get

This command-line option indicates to IAS the default branch indirect=br\_tar target for indirect unannotated branches. It is relevant for virtual register allocation. Values for br\_target are:

exit exit is assumed to be the branch target

labels any label is assumed to be the branch target

**Default:** Exit is assumed.

**Examples:**

-ias -X explicit -a indirect=labels my file.s or -ias -a indirect=exit my\_file.s

-N us

This option enables an extended range of numbers, unifying both signed and unsigned numbers. IAS accepts the numbers between -64 and +127, as 7 bits long.

**Default:** The range of a 7-bit number is either between -64 and +63, or between 0 and +127.

Example: ias -N us my\_file.s

# Dependency Violations and Assembly Modes

This section describes dependency violations and how the Intel® Itanium(TM) assembler (IAS) helps you avoid them in your code.

A violation of data dependency results from two instructions within an instruction group accessing the same Itanium architecture resource, including resources that appear as implicit operands. Dependency violations result in architecturally undefined behavior. The assembler can detect and eliminate dependency violations that occur within instruction groups, depending on its mode.

You can write code in explicit mode, thereby taking responsibility for bundling and stops (;;). You can also use automatic mode where IAS automatically bundles your code ands add stops to solve dependency violations. IAS allows you to mix modes in the one file. For an explanation of bundles and stops, see the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide* or the Features section in this document.

When you choose to write code in explicit mode, IAS reports any dependency violations it encounters. The easiest way to solve them is by inserting a stop. Some reports may not be accurate, in which case you have at your disposal a range of annotations and commands, explained later in this section.

For a complete description of data dependencies, see the *Intel® Itanium(TM) Architecture Software Developer's Manual* and the DVLoc for Scheduling Library.

This section includes:

- Assembly Modes

- Mode Exmples

- Serialize and Memory Synchronization Instructions

- Avoiding False Reports

- Predicate Relation Analysis

## **Assembly Modes**

IAS reads and processes assembly code in one of two modes: explicit or automatic. Use explicit mode if you are an expert user with profound knowledge of Itanium(TM) architecture and performance is important. Use automatic mode if you are a novice user or performance is not important.

#### **Automatic Mode**

Automatic mode is appropriate for implementation of non-performance-critical code. In this mode, you can write linear code without specifying bundle boundaries and without worrying about architectural dependencies. IAS bundles the code and inserts stops (;;) when needed. IAS ignores all your stops and dependency violations-related annotations.

Automatic mode is the default initial mode. The initial mode can be changed to explicit mode with the command-line option -X explicit.

IAS issues an error if it encounters a curly bracket after the mode directive .auto.

IAS strives to insert a minimal number of stops.

#### Note:

In automatic mode, the assembler ignores the .pred.rel annotation.

#### **Explicit Mode**

Explicit mode is suitable when writing performance-critical code.

In this mode, you must avoid dependency violations by inserting stops and annotations in the code. IAS checks the correctness of this code for dependency violations and returns an error if it detects potential or certain problems.

You can set explicit mode in the following ways:

insert curly brackets ( { , } ) signifying bundle boundaries, while in default automatic mode (Note that a curly bracket following a .auto directive causes an error.) insert the directive .explicit

use the command-line option -X explicit, which changes the default mode from automatic to explicit.

When you enter a new code section, IAS sets the mode back to the default.

If you write explicit code without bundle boundaries, IAS adds them. However, you are responsible for stops and annotations. Annotations define relations between predicate registers and other run-time values. See Avoiding False Reports.

#### Behavior of IAS

You can mix code from both modes in the one file. IAS provides you with several ways to switch between the modes:

- use the command-line option -X explicit

- use the mode directives: .auto, .explicit, and .default

- when the initial default mode is automatic, allow IAS to switch according to code syntax

If there are no bundles, IAS bundles the code, adds nops for correct bundling, and add stops to avoid dependency violations.

The directives .explicit and .auto override the initial default mode for the current code section.

The directive .default returns IAS to the initial default mode.

If IAS encounters a mode directive within an explicit bundle, IAS issues an error.

IAS automatically inserts a stop when it switches between modes.

For an explanation of how to write Itanium architecture code and avoid dependency violations, see <u>Avoiding False Reports</u>.

## **Mode Examples**

#### **Explicit Mode**

When IAS encounters the following code in explicit mode, it registers a dependency violation error.

The directive .default causes the mode to switch to the default initial mode defined in the command line; which in this case is automatic.

#### **Automatic Mode**

In automatic mode, using similar code to the previous example, IAS ignores existing stops and inserts stops between dependent instructions, as in the following example:

```

.auto

(p1)mov r1 = r4

;;;

; IAS ignores this stop

(p2)mov r6 = r2

ldfps f4,f5 = [r4]

; IAS inserts a stop to avoid WAW error on f4

fabs f4 = f7

```

#### **Initial Default is Automatic Mode**

In the following example, the default mode is automatic:

```

(p1)mov r1 = r4

; IAS inserts a stop here

(p2)mov r1 = r2

{ ; IAS inserts a stop here

; IAS treats this code as explicit

ldfps f4,f5 = [r4]

fabs f4 = f7 // write-after-write error

}

```

## **Serialize and Memory Syncronization Instructions**

The serialize (srlz) and memory synchronization (sync) instructions have the following constraints regarding instruction groups:

- The serialize instruction (srlz.i or srlz.d) must be located in the instruction group following the operation to be serialized.

- Operations dependent on the serialization must be in an instruction group after the srlz.i.

- Operations dependent on the serialization must follow the srlz.d, but they can be in the same instruction group as the srlz.d.

- The sync.i instruction and previous Flush Cash operation must be in separate instruction groups.

For safety's sake, IAS in automatic mode inserts stops before srlz.d and sync.i instructions, and both before and after the srlz.i instruction. In explicit mode IAS does not indicate errors when stops are missing.

## **Avoiding False Reports**

In some cases, when in explicit mode IAS falsely reports a dependency violation. IAS cannot calculate all the properties of the code when information is lacking.

The simplest way to avoid false register dependency errors is by using stops. Place a stop (;;) between the two instructions causing the violation dependency. This approach is simple and always works, but might result in performance degradation.

Use the following annotations to assist IAS in analysis of dependency violations to solve false reports, without sacrificing performance:

- .pred.rel

- .reg.val

- .mem.offset

#### Note:

Annotations supply additional information that assists IAS' analysis of apparent dependency violations.

For a description of annotations' syntax, see the Intel® Itanium(TM) Architecture Assembly Language Reference Guide.

The examples that follow show some typical situations where adding annotations helps avoid false reports.

## **Predicate Relation Analysis**

IAS analyzes predicate relations to determine dependency violations between pairs of predicated instructions. The following example displays a write-after-write dependency violation:

```

(p1) add r5 = 8, r6 (p2) add r5 = r7, r0

```

To understand how IAS performs predicate analysis, see <u>Predicate Analysis</u>.

The compare instructions define predicate register values and may result in definition of predicate relations.

To pass on information about predicate relations, use the predicate relation annotation .pred.rel.

The annotation .pred.rel takes the following forms:

"mutex" The mutex form defines a mutually exclusive relation.

"imply" The imply form defines an implication relation.

"clear" The clear form removes mutex and imply relations, as described

below.

When conflicting instructions follow an entry point, IAS ignores all existing predicate relations defined before the entry point.

An entry point is any of the following:

- a label, whether local, global, or temporary

- the address of the bundle following a br.call instruction

- the target of a direct branch

Use the predicate relation annotation to define the relations between predicates and prevent dependency violation errors.

This section includes:

- Compare Instructions

- Mutex Form of the .pred.rel Annotation

- Implication Form of the .pred.rel Annotation

- Clear Formof the .pred.rel Annotation

- Mutex Relation Not Created with a Single Compare

- Instructions Separated by a Predicate Branch

- Safe Across Calls

- Indirect Access to Register File

- st8.spill and ld8.fill in the Same Instruction Group

#### **Compare Instructions**

The compare instructions (cmp, tbit, fclass, and fcmp) define predicate values. They precede the predicated instructions. The compare instructions indicate to the assembler that the named predicate registers are mutually exclusive. They override any other defined mutex relations between the destination predicate registers and other predicate registers.

These examples all show the use of the cmp instruction for simplicity. Use the tbit, fclass, and fcmp instructions for the same effect.

In the example below, the cmp instruction states that P1 and P2 cannot both be true at the same time, thereby avoiding a violation dependency error.

```

mp.lt p1, p2 = r13, r0;;

(p1) dd r5 = 8, r6

(p2) dd r5 = r7, r0

```

The cmp instruction overrides the mutex relation between the destination predicate registers and all the other predicate registers. For example:

```

mp.lt p1,p2 = r13,r0;;

; p1 and p2 are mutually exclusive

mp.lt p1,p3 = r12,r11;;

; the mutex relation between p1 and

; p2 is destroyed by cmp

(p1) dd r5 = 8, r6

(p2) add r5 = r7, r0 // WAW error

```

#### **Mutex Form of the .pred.rel Annotation**

```

Format: .pred.rel "mutex" p1, p2 [,&ldots;]

where

p1, p2 ... are predicate registers

.pred.rel "mutex" informs the assembler that only one of the specified predicate

registers is true, or all are false. For example:

pred.rel "mutex" p1 p2 p3

```

```

.pred.rel "mutex", p1, p2, p3

; p1, p2, and p3 are mutually exclusive or all zero

(p1)add r5 = 8, r6

(p2)add r5 = r7, r0

(p3)add r5 = r14, r0

```

The mutex form is unordered, meaning that the order in which the predicates appear is not important.

The mutex form does <u>not</u> override predefined mutex relations between the destination predicate registers and other predicate registers. For example:

```

.pred.rel "mutex",p1,p2

.pred.rel "mutex",p1,p3

.pred.rel "mutex",p2,p3

; p1,p2 and p3 are mutex

(p1)mov r4=r5

(p2)mov r4=r6

(p3)mov r4=r7 // no WAW error is reported

```

#### Implication Form of the .pred.rel Annotation

#### **Format:**

```

.pred.rel "imply" p1, p2

where

p1, p2 are predicate registers

```

The .pred.rel annotation of the form "imply" informs the assembler that if the first predicate is true then the second one is also. No assumptions are made when the first predicate is false; the second predicate's value is undetermined. The implication form is ordered, meaning that the order of the predicates is important.

In the next example, if P1 is true, then P2 is also true.

```

.pred.rel "imply", p1, p2

(p1)mov r4=r5

(p2)br.cond.dpnt.few b0

mov r4=r5

; WAW on r4 is not reported as p1 implies p2

```

The implication form is a transitive relation. If P1 implies P2 and P2 implies P3, so P1 also implies P3.

#### Clear Form of the .pred.rel Annotation

The .pred.rel annotation of the form "clear" erases predicates relations. If you specify the predicate register P1, IAS erases all the mutex relations containing P1, and all the implication relations in which P1 is the implicating predicate register. If you do not specify any predicate registers, IAS takes this as a shortcut to naming all the predicate registers.

#### Format:

```

.pred.rel "clear" [p1[,p2[,&ldots;]]]

where

p1, p2 are predicate registers

For example:

.pred.rel "clear" p1; clears all the p1 relations

.pred.rel "clear"; clears all predicate relations

```

The following example uses both mutex and implication relations. The form "clear" has different effects depending on the relations.

#### Mutex Relation Not Created with a Simple Compare

In the following code, P1, P2, and P3, are mutex since R10 can have only one value at a time. IAS fails to interpret the inherently mutex relation and reports three WAW dependency violations.

```

cmp.eq p1=1,r10

cmp.eq p2=2,r10

cmp.eq p3=3,r10;;

(p1) mov r4=r1

(p2) mov r4=r2

(p3) mov r4=r3

```

To resolve this, use the .pred.rel annotation of the "mutex" form:

```

cmp.eq p1=1,r10

cmp.eq p2=2,r10

cmp.eq p3=3,r10;;

.pred.rel "mutex",p1,p2,p3

(p1) mov r4=r1

(p2) mov r4=r2

(p3) mov r4=r3

```

## Instructions Separated by a Predicated Branch

In the following example, there are no dependency violations due to the unconditional compare. The instructions are numbered #1 through #6 for clarity.

The apparent WAW on R1 can never happen since instruction #2 and instruction #5 never execute in parallel. That is, instruction #2 executes (P2 true) implying that instruction #4 executes (P2 implies P1), and the code execution branches to L without reaching instruction #5.

The apparent WAW on R2 can only happen if instruction #4 does not execute and instruction #6 does. Since execution of instruction #6 (P3 true) implies execution of instruction #4 (P3 implies P1), the WAW never happens.

```

#1 (p1) cmp.eq.unc p2,p3=r1,r2;;

#2 (p2) mov r1=r10

#3 mov r2=r11

#4 (p1) br.cond.dpnt.few L

#5 mov r1=r12

#6 (p3) mov r2=r13

```

To avoid false reporting of WAW errors on R1 and R2, insert the "imply" form of the .pred.rel annotation:

```

(p1) cmp.eq.unc p2,p3=r1,r2;;

.pred.rel "imply",p2,p1 ; if p2 is true, p1 is true

.pred.rel "imply",p3,p1 ; same as above, with p3

(p2) mov r1=r10

mov r2=r11

(p1) br.cond.dpnt.few L

mov r1=r12

(p3) mov r2=r13

```

#### Safe Across Calls

The annotation .pred.safe\_across\_calls allows predicate relations to be retained, even after calls to other procedures. Use this annotation to specify which predicates should have their relations preserved. The scope of the annotation is within the current procedure or module.

You can specify several individual predicates and a range of predicates, all in the one statement.

#### Format:

```

.pred.safe_across_calls p1, p2, ...

```

where P1, P2, etc. can represent specific predicate registers or ranges of registers.

In the following example, if the .pred.safe\_across\_calls annotation is not included, IAS reports a dependency violation between two last instructions, as procedure foo may change the predicate values.

To clear the predicate relations defined by the annotation .pred.safe\_across\_calls, use as follows:

```

.pred.safe across calls "clear"

```

## **Indirect Access to Register File**

The existence of dependency violations may depend on general register values; for example, when accessing register files indirectly. In the following example, two different registers are accessed indirectly. IAS does not have information about the values of the index registers, so it reports a WAW error on pmd.

```

mov r1=2

mov r2=4;;

mov pmd[r1]=r11

mov pmd[r2]=r12

```

To resolve this, use the .reg.val annotation to inform IAS that the two writes to pmd access different registers:

```

mov r1=2

mov r2=4;;

.reg.val r1,2

mov pmd[r1]=r11

.reg.val r2,4

mov pmd[r2]=r12

```

#### st8.spill and ld8.fill in the Same Instruction Group

The instruction st8.spill writes to a specific bit in the UNAT application register, according to the accessed address in memory. The instruction ld8.fill reads a specific bit of the UNAT application register, according to the accessed address in memory. For more details see the *Intel® Itanium(TM) Architecture Software Developer's Manual*.

IAS cannot know the address of the accessed memory, so where no annotations are provided, it reports the following dependency violations:

- WAW for every pair of st8.spill instructions

- RAW for every ld8.fill instruction that appears after st8.spill in the same instruction group

In the following code, one WAW and two RAW dependency violations are reported, although the code assures that the accessed UNAT bits are different:

```

add r2=r1,8

add r3=r1,16;;

st8.spill [r1]=r11

st8.spill [r2]=r11

ld8.fill r12=[r3]

```

To avoid this false report, use a .mem.offset annotation before each st8.spill and ld8.fill instruction. The annotation must state the memory address location relative to some local arbitrary memory region, such as the current stack:

```

LOCAL_STACK_INDEX=0

add r2=8,r1

add r3=16,r1;;

.mem.offset 0,LOCAL_STACK_INDEX

.st8.spill [r1]=r11

.mem.offset 8,LOCAL_STACK_INDEX

.st8.spill [r2]=r11

.mem.offset 16,LOCAL_STACK_INDEX

.ld8.fill r12=[r3]

```

For further explanation of the .mem.offset annotation, see the Intel @ Itanium(TM) Architecture Assembly Language Reference Guide.

To understand how IAS performs predicate analysis, see Predicate Analysis.

## **Features**

This section describes the following Intel® Itanium(TM) Assembler (IAS) features:

- <u>Assembly Language Features</u> in brief, which are fully defined in the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide*

- <u>Complementary Features</u> specific to the Intel® Itanium architecture assembly tool.

## **Assembly Language Features**

IAS supports these Itanium(TM) architecture assembly language specification features:

- Instruction Set

- Bundling

- Instruction Groups

- Data Allocation

- Assembly Language Directives

- 64-bit Address Space

- Alignment

- Assignment Statements

- Aliasing

- Arithmetic Expression Handling

The following sections provide a short description of these features. See the *Intel*® *Itanium*<sup>TM</sup> *Architecture Assembly Language Reference Guide* for the full explanation of these features.

#### Instruction Set

IAS supports the full Itanium(TM) architecture instruction set, defined in the *Intel*® *Itanium(TM) Architecture Software Developer's Manual*.

#### **Bundling**

Itanium(TM) processors execute instructions in bundles. A bundle contains up to three instructions, and an associated template. The template defines which type of execution unit processes each instruction in the bundle.

IAS enables several levels of bundle definition:

- Explicit bundling and template definition. You define the bundle boundaries and the bundle template.

- Explicit bundling without template definition. You define the bundle boundaries; IAS chooses the best fitting bundle template.

• Implicit bundling. IAS chooses bundle boundaries and the bundle template by selecting the optimal code size arrangements.

At all the bundle definition levels IAS inserts required NOPs.

The bundling feature is fully defined in the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide*.

#### **Instruction Groups**

Itanium(TM) processors execute several instructions in parallel. Instructions that are allowed to execute in parallel are organized in instruction groups. An instruction group is a set of consecutive instructions that should have no interdependencies. The instruction group is terminated by a stop (;;). IAS supports explicit stops as defined in the Intel® Itanium(TM) Architecture Assembly Language Reference Guide.

IAS checks for data dependencies in instruction groups. An example of a data dependency is a write instruction following a read instruction to the same register. For more details on dependency violations, see <u>Dependency Violations and Assembly Modes</u>.

#### **Data Allocation**

IAS enables allocating and initializing space in memory. IAS supports these data types:

• integers 1, 2, 4, or 8 bytes long

• floating-point numbers 4, 8, 10 or 16 bytes long

• strings up to 1024 bits long

Data allocation is fully defined in the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide*.

## **Assembly Language Directives**

IAS supports all Itanium architecture assembly language directives except local label directives, which are described in the *Intel*® *Itanium(TM) Architecture Assembly Language Reference Guide*. The supported directives include the following operations or information:

- section control

- symbol control

- file inclusion

- bundle template selection

- debug information

- unwind information

#### **64-bit Address Space**

IAS supports 64-bit address space.

When using the -ilp32 command-line option (this is the default for COFF32 output file format), symbolic addresses are limited to 32-bit allocation (data4). IAS displays an error message when you attempt to use relocatable expressions at 64-bit allocations (data8).

This feature is fully defined in the *Intel*® *Itanium*(*TM*) *Architecture Assembly Language Reference Guide*.

#### **Alignment**

By default, IAS aligns bundles on 16-byte boundaries, and data elements according to their size.

IAS aligns each section according to the largest alignment request in the section. Bundles, data elements, or an .align directive create alignment requests.

The object file format limits section alignment. COFF32 object file format limits section alignment boundaries to 8 KB. The actual limitation depends on the linker alignment policy. See the *Microsoft\* Developer Studio*, *Visual C++\* User's Guide*, and *LINK Reference* for more information on the linker.

To disable automatic alignment in data allocation statements, add a .ua completer to the data allocation statement. For example:

data8.ua 0x855

Alignment is fully defined in the *Intel*® *Itanium(TM) Architecture Assembly Language Reference Guide*.

## **Assignment Statements**

Assignment statements enable the programmer to define a symbol by assigning it a value. This value may be a reference to another symbol, register name, or expression. See the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide* for more information.

## Aliasing

IAS supports aliasing of symbol names and section names. Aliasing is implemented as follows:

symbol names Aliased by an .alias directive. The alias name appears in the

symbol table of the output file.

section names Aliased by a .secalias directive. The alias name appears in the

symbol table of the output file. See the .secalias Directive section

for more information.

Aliasing is fully defined in the *Intel*® *Itanium*(*TM*) *Architecture Assembly Language Reference Guide*.

#### **Arithmentic Expression Handling**

IAS supports the use of arithmetic expressions for constants and addresses, using standard arithmetic notation. Arithmetic expressions can include symbols, numeric constants, and operators.

IAS supports expressions that access linker tables during run-time, through the use of several link-relocation operators. See the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide* for more information on link-relocation operators.

Input file constants are internally represented as signed 128-bit numbers. IAS makes all integer calculations with 128-bit precision, and floating point calculations (real numbers) in extended precision (long double).

## **Complementary Features**

IAS has several additional features not documented in the Intel® Itanium(TM) Architecture Assembly Language Reference Guide:

- IA-32 impe Instruction

- <u>instenc Pseudo-instruction</u>

- String Equation

- secalias Directive

- <u>Line Information for Debugging Tools</u>

- # line Support

- Predefined Symbols

- Virtual Registers Allocation

- <u>Unwind Information Generation</u>

#### IA-32 jmpe Instruction

IAS supports IA-32 to Itanium(TM) architecture transition instructions (jmpe) from within Itanium architecture assembly language files. When you assemble an Itanium architecture file with a jmpe instruction, IAS creates an IA-32 jmpe instruction, enabling the transition from IA-32 code to Itanium architecture code.

The following directives are available:

jmpe.next Jumps to the next 16-byte aligned address.

jmpe.abs address Jumps to the specified address, as a number

or as a relocatable expression.

jmpe.IA-reg32 Takes an indirect jump to the address

specified in the IA-32 register. For example:

jmpe.eax.

#### instenc Pseudo-instruction

This pseudo-instruction enables you to enter a 41-bit immediate number to a slot in a bundle. This immediate number may be recognized by the Itanium(TM) processor as an instruction. However, IAS does not check that the immediate number corresponds to a valid Itanium architecture instruction.

This pseudo-instruction is useful when you want to create executable code containing instructions that your current assembler version may consider illegal.

#### **Syntax**

instenc.completer imm41

where:

completer Defines the role of the instruction in the bundle.

These are this instruction's completers:

a ALU instruction

m memory instruction

i integer instruction

b branch instruction

f floating-point instruction

imm41 Is the immediate number corresponding to an

Itanium instruction.

#### Example

```

This example inserts a floating-point instruction into the bundle.

{ add r1 = r2, r3 instenc.f 0x1F423C02DA9 }

```

#### **String Equation**

The equation statement (==) that equates a symbol to a value or a register, can also equate a symbol to a string. For example:

```

save_file_name == @filename

or,

source_file == "my_file.s"

```

You cannot forward-reference a string equation statement.

```

.secalias Directive

```

The .secalias directive defines an alias for a section name. .secalias does for section names what .alias does for symbol names. See <u>Aliasing</u> section for more information.

Within the input file you reference the section by the section name. In the output file the section is referenced with its alias. Typical use of this directive is to identify a section with a name that is not a legal assembly identifier.

#### Note

You must define the section before you use .secalias to alias it.

#### **Syntax**

#### Example

This example shows the use of the .secalias directive to alias a section name.

```

.section sec1, "ax",

... "progbits"

.secalias sec1, "sec++"

...

.text

.xdata

...

sec1, 5

```

#### **Line Information for Debugging Tools**

Debug directives create line information used to create debug information in the object file. Each line information directive creates a debug record. The debug record points to the position of the code generated by the instruction following it. Two debug records cannot point to the same location. Therefore, make sure there are lines of code between two debug directives.

The line information reference in the debug record refers to the exact instruction slot in the bundle.

If you use the -d debug command-line option, IAS ignores the .bf, .ln, and .ef directives.

Use this general template to produce line information:

```

.file "source-file-name"

...

.proc entry [,...]

...

entry:

...

.bf entry, source-line-no

;

prologue code

;

.ln source-line-no

; assembly code

.ln source-line-no

;

assembly code

;

...

...

.ln source-line-no

;

ef entry, source-line-no, procedure-size

;

epilogue code

;

.endp [entry]

```

## #line Support

The #line directives define the line number of the next code line, and can also replace the file name for the object file. You can explicitly enter the #line directives, or they may be inserted by the preprocessor.

The #line definition impacts the diagnostic messages and assembly-level line information created when the -d line option is specified in the command-line option. See <u>Compilation Model</u> for more information.

These are the #line directives IAS recognizes:

#line line-no IAS treats the next line as the line-no line in the current file, regardless of the serial count.

#line line-no "filename"

IAS treats the next line as the line-no line in "file-name"; this file name replaces the previous

object file name.

This directive may also contain a comma between the operands.

#### **Predefined Symbols**

IAS provides three predefined symbols. Use them in the assembly language file:

@line is an integer specifying the current line number.

Usage example: data8 @line

@filename is a string specifying the current file name.

Usage example:

stringz @filename

@filepath is a string specifying the current path and filename.

Usage example:

stringz @filepath

#### **Virtual Registers Allocation**

Virtual registers allocation (Vral) allows use of symbolic names instead of register names. This feature replaces registers or groups of registers with meaningful names, making code

- simpler to write

- faster to read

- easier to maintain

When VRAL is activated, the assembler analyzes control flow and data flow, builds life ranges for each register, and replaces symbolic names with the user-allocated registers.

With one directive, VRAL can assign one name to a group of registers, allowing the assembler to handle the use of individual registers within the group. VRAL is then responsible for ensuring safe reuse of registers.

To allocate symbolic names to registers, use these directives:

- .vreg.allocatable

- .vreg.safe\_across\_calls

To declare register variables, use these directives:

- .vreg.var Family, Xcounter

- $^ullet$  .vreg.family LocalIntFamily, reg\_range

To undefine or redefine variables, use these directives:

- .vreg.undef Xcounter

- .vreg.redef Xcounter

The following annotations are useful when using Vral:

- .br.target annotation

- .entry annotation

- .bank switch annotation

This section includes:

- Allocate Registers

- Declare Variables

- Undefine and Redefine Registers

- Branch Target Annotation

- Register Value Annotation

- Bank Register Annotation

#### **Allocate Registers**

The .vreg.allocatable directive assigns registers for allocation, thereby making them available for VRAL from this point in this procedure. There can be more than one allocation directive in each procedure. Values of these registers are not ensured preserved across calls. This directive has the following syntax:

```

.vreg.allocatable reg\_range where

```

reg\_range can be a single register, a range of registers, or both.

In the following example, integer registers 14 through 26, and register 30 are assigned: .vreg.allocatable r14-26, r305

Alternatively, the .vreg.safe\_across\_calls directive informs the assembler that the named registers are preserved across calls. This directive assurs the assembler that branches to external procedures following this directive do not access or corrupt the named registers. The directive has the following syntax:

```

.vreg.safe_across_calls reg_range

where

```

reg\_range is not restricted to the registers allocated in the .vreg.allocatable directive. Example:

```

.vreg.safe_across_calls f16, f18-f21

```

#### **Declare Variables**

```

Use the following syntax to declare register variables:

```

Each variable belongs to a single register family. Use the following syntax to define families:

#### **Examples:**

```

.vreg.family MyLocalFamily, loc0-loc3

.vreg.family FpUsedRegisters, f17-f25

```

A register may belong to more than one family. Each family may contain registers of only one type (int, float, etc.).

There are four predefined families in the assembler syntax:

@int all registers from r1 to r127

@float all registers from f1 to f127

@branch all registers from b0 to b7

@pred all registers from p1 to p63

#### **Undefine and Redefine Registers**

VRAL directives can be used only within the procedure, between the directives .proc and .endp. The variables declared by the directives are valid from their declaration till the end of the procedure or until they are undefined or redefined.

Use the following syntax to undefine variables, so the variable names can be used again within the procedure:

```

.vreq.undef Xcounter

```

Use the following syntax to redefine variables, with no need for undefining. Notice there is no opportunity to specify a different family:

```

.vreq.redef Xcounter

```

An example of the Virtual Registers Allocation (VRAL) directives usage is shown as follows.

#### **Virtual Registers Allocation Example**

```

.proc foo

.vreq.allocatable r19-r21, r27

.vreq.safe across calls r20, r21, p5-p6

.vreg.var @pred, HL1, L1H, HL2, L2H, HX, XH

.vreq.family MyGlobals, r19-r20

.vreg.var MyGlobals, High, Low1, Low2

foo::

alloc loc0 = 3,1,1,0

ld8 High = [in0]

ld8 Low1 = [in1];;

cmp.gt HL1, L1H = High, Low1

(L1H) br.cond.sptk.few LE

sub out0 = High, Low1

GT: add r22 = 32, r5;

END:

cmp.eq HX, XH = High, r22

(HX) br.call.spnt.many rp = bar;;

(XH) st8 [r23] = High

br.ret.sptk.clr b2

LE: ld8 Low2 = [in2] ;;

cmp.qt HL2, L2H = High, Low2

(HL2) sub out0 = High, Low2

(HL2) br.cond.sptk.few GT ;;

mov out0 = 0

br.cond.sptk END

.endp foo

```

#### **Branch Target Annotation**

The branch target annotation .br.target precedes an indirect branch and explicitly provides the assembler with the branch target address for the branch instruction. This annotation applies only to the branch instruction that immediately follows the annotation. The .br.target annotation has the following syntax:

The following examples illustrates a branch target annotation.

```

Using the Branch Target Annotation 1

```

```

.br.target a=0.6, b, @fallthrough=0.2, @external=0.1 Using the Branch Target Annotation 2

```

```

br.target Target002

(p4)br.cond.sptk.many.b1

```

where

Target 002 Is the name of a label in the procedure.

#### **Register Value Annotation**

The register value annotation .reg.val informs the assembler of the contents of a register. It is used for dependency violations detection.

The annotation has the following syntax:

```

.reg.val reg, val

where:

reg Represents any integer register from r0 to r127.

val Is any real number.

```

Example below illustrates a .reg.val annotation.

#### **Using the Register Value Annotation**

```

.reg.val r5,3

```

#### **Bank Register Annotation**

By default, the assembler assumes that the register bank at the entry point is bank 1. To overwrite this default use the .bank directive. It is necessary only for procedures that contain a bsw instruction, for VRAL.

This annotation makes it clear to the assembler to which bank of registers the instructions refer

```

The .bank switch annotation has the following syntax:

```

```

.bank n where: n represents 0 or 1.

```

Example that follows illustrates a .bank annotation.

#### **Using the Bank Switch Annotation**

```

.proc A //entry annotation

A:

.bank 0

...

bsw.1

...

bsw.0

...

.endp

```

#### **Unwind Information Generation**

IAS applies static analysis to procedure code to automatically generate unwind records. Use this feature when a procedure as an intermediate element must provide safe propagation of the stack unwinding process from the called function to the unwind handler in the caller procedure.

The assembler builds unwind information for all procedures in the file, starting from the procedure's first entry point and continuing through to .endp.

When the static analysis is not complete; for example, an indirect branch is

unaccompanied by branch target annotation, IAS sends a warning message and then attempts to simplify the analysis by assuming that the procedure has one prologue and multiple epilogues. This approach works in most cases. If this is not successful, IAS issues an error message.

The unwind generator is based upon the Itanium(TM) architecture software conventions. See the *Software Conventions and Runtime Architecture Guide*. Invoke unwind generation using the -X unwind command-line option. When you use this flag, IAS ignores all unwind directives and issues a warning.

## **Diagnostic Messages**

When IAS encounters suspicious or incorrect input, or fails at some operation, it provides a diagnostic message. You can receive the diagnostic messages either on the screen, or send them to a file. See Error Handling for more information.

This section describes the syntax of diagnostic messages, and describes the diagnostic messages in numeric order.

#### **Note:**

IAS displays diagnostic messages according to the order of their corresponding lines in the source code. This order is not necessarily the order in which they were detected. Therefore, a diagnostic message of the derivative error may appear before the diagnostic message from the original error.

#### This section includes:

- Diagnostic Message Types

- Diagnostic Message Syntax

- Fatal Error Messages

- Error Messages

- Warning Messages

## **Diagnostic Message Types**

IAS sends these types of diagnostic messages:

fatal error messages IAS detected incorrect input that causes termination. IAS does

not produce an object file. Fatal error message numbers have

this format: A1xxx.

error messages IAS detected incorrect input. Execution continues. However,

IAS does not produce an object file. Error message numbers

have this format: A2xxx.

warning messages IAS detected legal, but suspicious input. Execution continues

and IAS produces an object file. Warning message numbers

have this format: A3xxx.

## **Diagnostic Message Syntax**

A diagnostic message specifies the location of the error, its type, and a short description of the error, as described below and shown in the Figure that follows the table.

Location The file name and line number information helps to locate the

exact part of the code that needs correction. In some cases the

location shows the detection of a derivative error.

Severity This information indicates the severity of the error.

Message number IAS message numbers are prefixed by an A. Use the message

number to locate its description.

Message text This text provides a one line explanation of the incorrect or

suspicious input.

Figure below shows an example of an error message, and specifies the message elements.

#### **Diagnostic Message Syntax Example**

### **Diagnostic Message Format**

This is the format of the diagnostic message descriptions:

\_\_\_\_\_

### Message Number Text of the message

Additional description of the message.

## **Fatal Error Messages**

This section describes fatal error messages. A fatal error causes immediate IAS termination without creating an object file. These are the fatal error messages IAS may display:

\_\_\_\_\_

A1012 cannot open input file file

IAS could not open this file. This fatal error message is usually due to an incorrect file name or path.

A1013 cannot open input file *file* included from *file* (*line*) IAS could not open this file. This fatal error message is usually due to an incorrect file name or path in the .include directory.

\_\_\_\_\_

A1014 cannot open registers allocation log file file

IAS could not open the file that lists the results of virtual registers allocations. Check that the file name with a suffix .vra is not in use. Delete any read-only files with the suffix .vra.

A1015 creation of section section failed: reason The assembler could not create the section, for the reason specified. A1018 too many errors: number The maximum permitted number of errors was exceeded, so execution terminated. You can configure the number of permitted errors with the  $-\mathbb{E}$  n command-line option. A1020 section stack underflow The .popsection directive operates on an empty stack. See the *Intel® Itanium(TM)* Architecture Assembly Language Reference Guide for more information on this directive. A1021 unable to open file as an error file IAS could not open the file designated in the command-line as the diagnostics file. A file with an identical name may be locked by another procedure. A1022 command-line option is missing an argument Usage message This command-line option is missing an argument. This fatal error message also provides the IAS command-line usage message. See Command-line Options for more information on IAS command-line usage. A1025 unknown command-line option option Usage message IAS does not recognize this command-line option. This fatal error message also provides the IAS command-line usage message. See <u>Command-line Options</u> for more information. A1026 option command-line option is incompatible with subargument sub-argument usage message The specified sub-argument is not valid for this command-line option. This fatal error message also provides the IAS command-line usage message. See Command-line Options for more information on the command-line options and their sub-arguments. A1027 .include directive has illegal placing/format This include directive is incorrect. This fatal error message may be caused by entering a

file name operand that is not a string. See the Intel® Itanium(TM) Architecture Assembly Language Reference Guide for more information on this directive.

An example of code that generates this message:

allocatable registers from family family

.include data.s

A1050 virtual register allocation failed: not enough

IAS needs more registers than have been allocated by the virtual register allocation directives.

A1099 nesting level (number) of .include directive exceeded for included file file

This .include directive is nested beyond the IAS nesting limit. IAS allows up to 20 nested levels.

\_\_\_\_\_

## **Error Messages**

This section describes the error messages. An error does not terminate IAS execution. However, it does prevent object file production. These are the error messages IAS may display:

\_\_\_\_\_

A2000 too long symbol name

The symbol name may not be longer than 4096 characters.

**A2023** there should be a prologue region in the function This directive requires a prologue code region in the function.

A2024 the personality routine is not defined for the language specific data

This directive requires defining a personality routine definition before the directive. Add a .personality directive before the .handlerdata directive. See the *Intel® Itanium(TM) Architecture Assembly Language Reference Guide* for more information on these directives.

A2025 directive ".proc" is not allowed within section ".xdata."

You cannot put a .proc directive in an .xdata section.

A2026 section switch is not allowed within handlerdata

You cannot switch sections in a handlerdata region.

**A2027** debug directive points outside the function An operand of the *debug* directive points outside the current function.

A2028 directive is allowed only within an explicit bundle This directive is legal only when specified within an explicit bundle. Place this directive

in between the two curly brackets " { " and " } ".

**A2029** *directive* is not allowed within an explicit bundle. This directive is not legal when specified within an explicit bundle. Make sure this directive is not placed between the two curly brackets " $\{$ " and " $\}$ ".

region

A2030 misplaced or missing '}' There is a curly bracket mismatch. Check preceding bundle's curly bracket structure. A2031 Unclosed parenthesis at start-of-statement This statement starts with an open parenthesis token " (". However, the close parenthesis ") " is missing. This statement may have an unclosed qualifying predicate. A2032 Unexpected *element* instead of predicate register Something other than a predicate register is specified in the location reserved for the predicate register. An example of correct usage: (p62) add r2 = r3, r6In this example P62 is the predicate register. An example of code that generates this error message: (p64) add r2 = r3, r6The predicate registers range is P0 - P63. A2033 Unexpected element instead of tag Something other than a tag is specified in the location reserved for tags. An example of correct usage: .save pr, r3, T [T:] mov r3=pr A2034 Unexpected token at end-of-statement: token The statement ends with an unexpected token. Delete or change the token. An example of code that generates this error message: add r1=r2,r3, A2035 invalid token: token This token is invalid. An example of code that generates this error message: add r1=r2,r3! **A2036** illegal usage of reserved register: register This register is a reserved register. Use a different register. An example of code that generates this error message: mov r5=ar8 **A2037** Unexpected token at start-of-statement: token This token is not valid at the start of the statement. Delete or move the token. An example of code that generates this error message: ) add r1=r2,r3

This error message may also be the result of a misspelled mnemonic. An example of a misspelled mnemonic that generates this error message:

br.cal b5=L

L:

\_\_\_\_\_

A2038 symbol/section already aliased as name

This symbol or section cannot be aliased at this stage, since it is already aliased as something else.

\_\_\_\_

A2039 label already defined: label

This label cannot be defined at this stage, since it is already defined elsewhere. Use a new label for this definition.

\_\_\_\_\_\_

A2040 Unexpected token token

The specified token is not expected in this location.

**A2042** symbol symbol for definition type is already defined This symbol is already defined elsewhere. Use a new name for this definition. An example of code that generates this error message:

L:

L=8

\_\_\_\_\_\_

${\bf A2047}$  unexpected character character in string hexa-escapesequence

The hexa-escape sequence contains an unexpected character. Hexa-escape sequences can contain digits 0-9 and/or letters A-F.

Examples of correct hexa-escape sequences are:  $\xapprox$  are  $\xapprox$  D9.

1 1

A2048 illegal bundle brace in automatic mode

IAS encountered a curly bracket ({) or (}) while in automatic assembly mode. Automatic mode was specified with the .auto directive.

\_\_\_\_\_

**A2049** relocatable expressions based on symbols symbol and symbol from different sections cannot be subtracted. These relocatable expressions are from different sections. To subtract two relocatable expressions, they must originate in the same section.

\_\_\_\_\_\_

A2050 cannot subtract relocatable expressions based on an external or common symbol

To subtract two relocatable expressions, they must be based on symbols defined in the same section. One or both of these relocatable expressions is probably based on an external or common symbol.

A2051 wrong operand parenthesis structure

The operand parenthesis structure is incorrect.

An example of code that generates this error message: nop ((5+3)

\_\_\_\_\_

A2052 wrong operand bracket '['']' structure

The operand bracket structure is incorrect.

An example of code that generates this error message:

ld8 r6 = [r4]

\_\_\_\_\_\_

**A2055** illegal argument [argument-type] for unary-operator operator, or misplaced/missing operator

This argument-type is not legal for the specified unary operator.

An example of code that generates this error message:

and r3=r2,+r5

\_\_\_\_\_

A2056 missing arguments for binary-operator: operator

This binary-operator is missing arguments.

An example of code that generates this error message:

mov rr[] = r6

\_\_\_\_\_

**A2057** illegal argument-pair [left: argument right: argument] for binary-operator operator, or misplaced/missing operator. These arguments cannot operate together. A typical mistake causing this error message is the use of a binary operator with at least one operand that is not valid for this operator. An example of code that generates this error message: or r4 = dbr[f4], r6

\_\_\_\_\_

$A2061 \; \text{a}$  sequence of unary-operator operator and element is illegal

This unary-operator cannot follow the specified element. An example of code that generates this error message: add  $r1 = \sim$ , r2

A2063 a sequence of hinary-operator operator and operands

A2063 a sequence of binary-operator operator and operands operand1 and operand2 is illegal

This binary-operator cannot follow the specified elements.

There may be a misplaced operator, for example: or r3 = 45+, r6 instead of the intended: or r3 = 4+5, r6

\_\_\_\_\_\_

A2065 wrong operand syntax

The operand syntax of this code line is incorrect.

In some cases, you may receive this error message when the cause is illegal operand combination. See error messages <u>A2069</u> and <u>A2070</u> for more information.

A2066 missing operator [possibly intended binary +/- taken as unary]

An operator is missing. There may be a misplaced operator, for example: 2\*-3 5 instead of the intended: 2\*3-5

Another possibility is a missing comma between operands, for example:

add r1 = r2 r3 instead of the intended code: add r1 = r2, r3.

A2067 incorrect tag usage: tag [might need to use label instead]

This tag is incorrect. Try replacing the tag with a label.

**A2068** value of operand operand number for element is not available when needed

This operand value is not available at the stage when it is needed. IAS cannot make forward references of this kind.

An example of code that generates this error message:

.skip L1-L2

L1: data8 1

L2:

\_\_\_\_\_\_

#### A2069 illegal operand combination for element

There is a mismatch between the mnemonic and the operands of this instruction. Several causes for this error message are: a missing operand, an incorrect operand type, an invalid register name that is interpreted as a symbol, or an incorrect choice of mnemonic.

A2070 illegal operand operand for element

This operand is not suitable for the specified element.

•

A2072 invalid section attribute: attribute

This section attribute is not valid. Section attributes depend on the Object Module Format (OMF). Several valid attributes are: a, w, x and s.

A 2002

**A2073** more than one comdat section flag defined: *flag* A comdat section can have only one comdat-flag defined. These are some of the possible flag definitions: D, S, E or Y. The flags are case-sensitive.

A2074 comdat flag is only applicable for comdat section

This comdat flag is defined for a non-comdat section.

A2075 comdat section flag not defined

A comdat section must have one comdat-flag defined. These are some of the possible flag definitions: D, S, E or Y. The flags are case-sensitive.

A2076 comdat section section associative symbol is not defined The comdat section must have at least one label. A2077 invalid section type: type This section type is not valid. These are the possible section types: proqbits, nobits, comdat and note. A2078 absolute sections section [address to address] and section [starting at address] overlap There is an overlap between the two specified absolute sections. A2079 absolute section section [starting at address] exceeds the 64-bit limit by value This absolute section exceeds the 64-bit address space limit. The specified value indicates how far the limit is exceeded.  $\mathbf{A2080}$  relocatable expression for element requires -p32 or -M ilp32 command-line options This relocatable expression conflicts with the current compilation model command-line option. See Compilation Model for more information. A2081 nobits section section cannot be written to There is an attempt to write to this nobits section. You cannot write to nobits sections. To correct this, do one of the following: delete the data in the nobits section, change the section type to progbits, or replace the data with a .skip directive. A2082 nobits section section contains data The nobits sections cannot contain data. To correct this, do one of the following: delete the data in the nobits section, change the section type to progbits, or replace the data with a .skip directive. A2083 integer constant token does not fit in number bits: token This input number token contains more bits than permitted in an integer constant. A2084 integer number does not fit in number bits: number This number is too big for this instruction. This number may be the result of an internal calculation.

**A2086** alignment request is too big: alignment Alignment requests are limited to 232-1.

**A2087** alignment request is not a power of 2: alignment An alignment request must be a power of 2.

A2088 symbol symbol is undefined

This symbol does not appear in the object file symbol table. A global or weak symbol must be either defined or declared. A local symbol must be defined.

**A2089** illegal global declaration of assigned symbol: *symbol* A declared symbol that appears in the object file symbol table cannot be assigned. You can use an equate (==) statement instead.

An example of code that generates this error message:

```

B = 8

.global B

```

A2090 assigned/equated symbol symbol cannot be used in statement

The use of this symbol in this statement conflicts with the symbol assignment or equation.

An example of code that generates this error message:

```

A == L

L:

.weak A = S

S:

```

A2091 symbol symbol is undefined

The symbol is not defined.

**A2092** symbol size of *symbol* exceeds 32-bit word size The size of the common symbol exceeds the 64-bit limit.

**A2093** symbol symbol is already bound as binding. This symbol's binding is already declared. You cannot redefine a symbol's binding.

**A2094** symbol size of *symbol* is already set to *size* This symbol's size is already declared. You cannot redefine a symbol's size.

A2095 symbol type of symbol is already set to type This symbol's type is already declared. You cannot redefine a symbol's type.

**A2096** type is an illegal type for symbol symbol This type is not one of the possible symbol types: @notype, @object and @function.